# EXTREME FINE-GRAINED PARALLELISM ON MODERN MANY-CORE ARCHITECTURES

# BY POORNIMA NOOKALA

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the Illinois Institute of Technology

| Approved |         |  |

|----------|---------|--|

| TT       | Adviser |  |

Chicago, Illinois December 2022 © Copyright by

POORNIMA NOOKALA

December 2022

#### ACKNOWLEDGEMENT

First and foremost, I am incredibly grateful to my supervisor Dr. Ioan Raicu for his continuous support and invaluable guidance throughout my PhD. I am also extremely thankful to Dr. Robert Harrison for his treasured support and for advising my research work at Stony Brook University. Dr.Raicu and Dr.Harrison have been monumental in shaping my PhD and I can't thank them enough.

I would like to offer special thanks to my dissertation committee: Dr. Kyle Hale, Dr. Stefan Muller and Dr. Jia Wang. I would like to extend my sincere thanks to Dr. Kyle Hale and Dr. Stefan Muller from Illinois Institute of Technology and Dr. Peter Dinda from Northwestern University for helping me develop the core idea behind the thesis. I would also like to express my gratitude to Dr. Kyle Chard for help in polishing my papers. In addition, I would like to thank all my colleagues and collaborators for their time spent and efforts made in countless meetings, brainstorming sessions, and running experiments. This dissertation could not have been completed without the consistent encouragement and support from my husband Ram Karri. My appreciation also goes out to my children, my family and friends for their encouragement and support all through my studies.

I would like to acknowledge the support from National Science Foundation (NSF) for this work under grants OAC-2107548/2107283, CCF-1757964, CCF-1461260, CCF-1757970, CNS-1730689 at Illinois Institute of Technology and OAC-1931387 and ACI-1450344 at Stony Brook University.

#### AUTHORSHIP STATEMENT

I, Poornima Nookala, attest that the work in this thesis is substantially my own.

In accordance with the disciplinary norm of Computer Science (see IIT Faculty Handbook - https://web.iit.edu/general-counsel/faculty-handbook, Appendix S), the following collaborations occurred in the thesis:

I am extremely grateful to Dr. Ioan Raicu for his guidance and continuous support throughout my PhD journey. I will be forever grateful to Dr. Robert Harrison for giving me the opportunity to be part of the TTG team and for the guidance and contributions of Dr. Edward F. Valeev from University of Tennessee, Dr. George Bosilca, Dr. Thomas Herault and Dr. Joseph Schuchart from the University of Tennessee at Knoxville for making TTG possible. Dr. Mahdi Javanmard, Dr. Martin Kong, Dr. Rezaul Chowdhury and Zafar Ahmad have been extremely helpful in exploring the limitations of fork-join parallelism. I would also like to thank Dr. Pavan Balaji from Meta for the brainstorming sessions for improvising my ideas on XQueue.

Last, but not the least, I would like to thank my fellow PhD student Alexandru Orhean, and Caleb Lehman and Jonathan Anderson (who were part of the Research Experience for Undergraduates (REU) program) for their contributions to this work. I would also like to thank Serapheim Dimitropoulos, Karl Stough, Pedro Valero-Lara, Fernando L Pelayo and Johan Jansson for their contributions to my early work in Many Task Computing.

The work in this thesis would not have been possible without the inputs and guidance from everyone listed here. I am extremely grateful to all!

#### TABLE OF CONTENTS

|                                                                                                | Page           |

|------------------------------------------------------------------------------------------------|----------------|

| ACKNOWLEDGEMENT                                                                                | iii            |

| AUTHORSHIP STATEMENT                                                                           | iv             |

| LIST OF TABLES                                                                                 | vii            |

| LIST OF FIGURES                                                                                | viii           |

| ABSTRACT                                                                                       | xii            |

| CHAPTER                                                                                        |                |

| 1. INTRODUCTION                                                                                | 1              |

| 1.1. Task-Based Parallelism                                                                    | 3<br>4<br>4    |

| 1.4. Dissertation Overview                                                                     | 10             |

| 2. HOW BAD IS CONCURRENT QUEUE PERFORMANCE ACROS MANY THREADS?                                 | SS 12          |

| <ul><li>2.1. Baseline Queue Performance</li></ul>                                              | 15<br>21<br>26 |

| 3. SCALABLE CONCURRENT QUEUES ON MODERN MANY-<br>CORE ARCHITECTURES                            | 28             |

| <ul> <li>3.1. XQueue: Lock-less Queueing Mechanism for Task-Parallel Runtime Systems</li></ul> | 29<br>34<br>51 |

| 4. X-OPENMP : EXTREME FINE-GRAINED TASKING USING LOCK-LESS WORK STEALING                       | 52             |

| 4.1. Motivation                                                                                | 53<br>55       |

|    | 4.4. Summary                                                                                          |

|----|-------------------------------------------------------------------------------------------------------|

| 5. | EFFICIENT EXECUTION OF DYNAMIC PROGRAMS USING DATA-FLOW BASED PARALLEL PARADIGM                       |

|    | 5.1. Motivation                                                                                       |

|    | <ul> <li>5.2. Background</li></ul>                                                                    |

|    | flow based Implementations                                                                            |

|    | 5.4. Experimental Results                                                                             |

|    | 5.5. Summary                                                                                          |

| 6. | THE TEMPLATE TASK GRAPH (TTG): AN DATAFLOW PROGRAMMING PARADIGM FOR IRREGULAR SCIENTIFIC APPLICATIONS |

|    |                                                                                                       |

|    | 6.1. Motivation                                                                                       |

|    | <ul><li>6.2. Template Task Graph</li></ul>                                                            |

|    | 6.4. Summary                                                                                          |

| 7. | RELATED WORK                                                                                          |

|    | 7.1. Many Task Computing                                                                              |

|    | 7.2. Concurrent queues                                                                                |

|    | 7.3. Parallel runtime systems                                                                         |

|    | 7.4. Load Balancing                                                                                   |

|    | 7.5. Dataflow Programming                                                                             |

|    | 7.6. Flowgraph Programming                                                                            |

| Q  | CONCLUSION AND FUTURE WORK                                                                            |

| Ο. | CONCEONION MILE I OT CHEE WORM                                                                        |

|    |                                                                                                       |

### LIST OF TABLES

| Ta | ble |                                                                                                                                           | Page  |

|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-------|

|    | 2.1 | Testbed for evaluation from the Mystic System                                                                                             | 16    |

|    | 3.1 | Application - number of tasks                                                                                                             | 42    |

|    | 5.1 | Ratio of the maximum estimated cache misses over the actual cache misses for the GE benchmark with problem size $8K \times 8K$ on SKYLAKE | . 102 |

|    | 6.1 | Software configurations                                                                                                                   | 122   |

### LIST OF FIGURES

| Figure |                                                                                                                                                                                                                  | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Directed Acyclic Graph (DAG)                                                                                                                                                                                     | 3    |

| 1.2    | Micro-architecture of the Entire MIC coprocessor [1]                                                                                                                                                             | 6    |

| 1.3    | Micro-architecture of the Entire MIC coprocessor [1]                                                                                                                                                             | 7    |

| 1.4    | Efficiency of Sleep workload using MIC by varying concurrency                                                                                                                                                    | 9    |

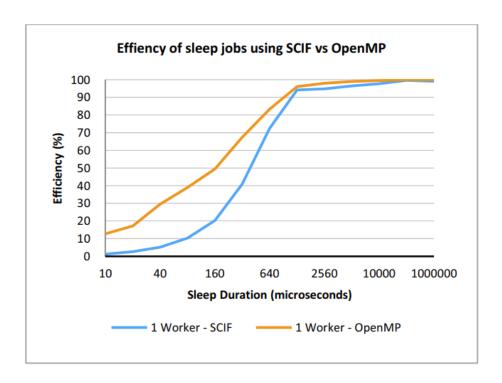

| 1.5    | Efficiency comparison of sleep workload using $\operatorname{OpenMP}$ and $\operatorname{SCIF}$ .                                                                                                                | 10   |

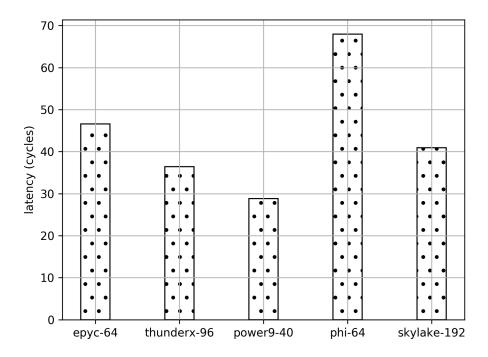

| 2.1    | Average latency of enqueue/dequeue operations on SPSC queue    .                                                                                                                                                 | 17   |

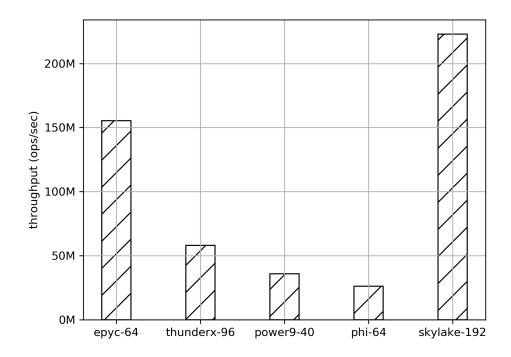

| 2.2    | Average throughput of enqueue/dequeue operations in millions(M) on SPSC queue                                                                                                                                    | 18   |

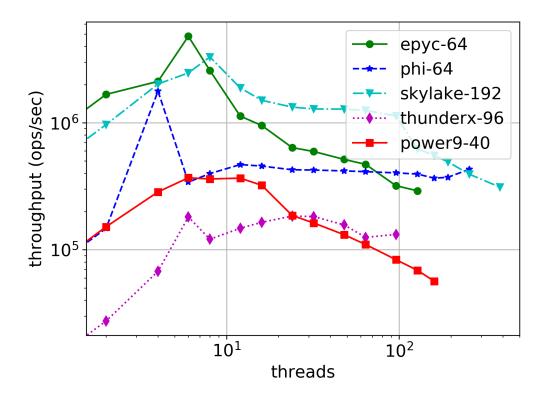

| 2.3    | Average latency of enqueue/dequeue operations on a lock-based queue. This graph is shows that simple lock-based queues don't scale beyond 8 threads on any modern processors                                     | 20   |

| 2.4    | Average throughput of enqueue/dequeue operations on lock-based queue. This graph shows that the throughput of a simple lock-based queue plateaus beyond 8 threads on modern processors                           | 21   |

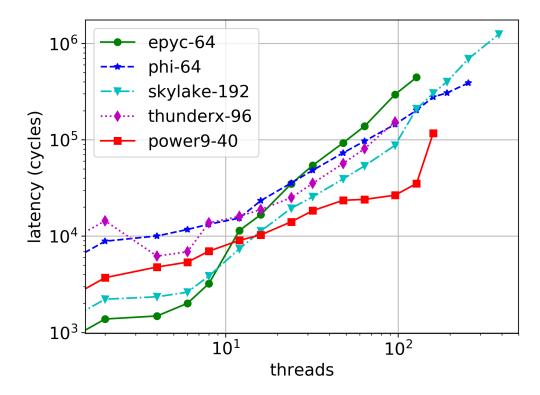

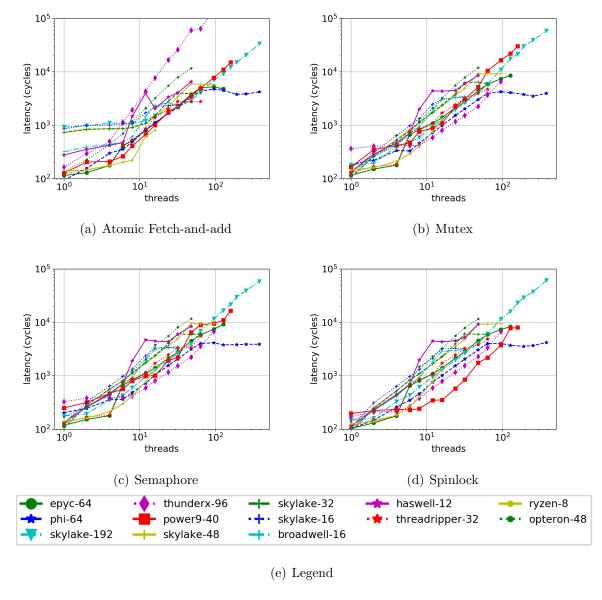

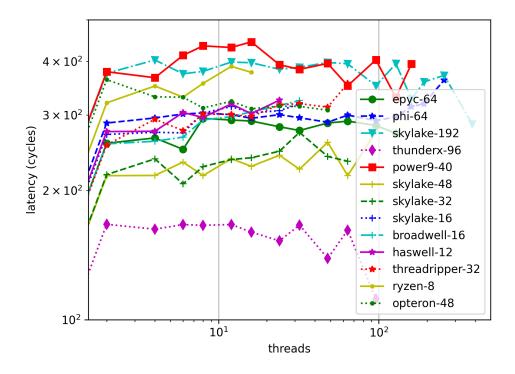

| 2.5    | Average latency of incrementing an integer using different synchronization mechanisms. Same trend is observed on all architectures where latency keeps increasing as threads are scaled up except Intel Xeon Phi | 25   |

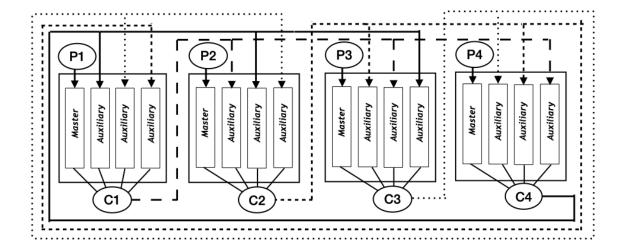

| 3.1    | Architecture of XQueue on a 4-core machine with 4 queues per consumer                                                                                                                                            | 30   |

| 3.2    | Average latency of enqueue/dequeue operations using XQueue (SPSC)                                                                                                                                                | ) 36 |

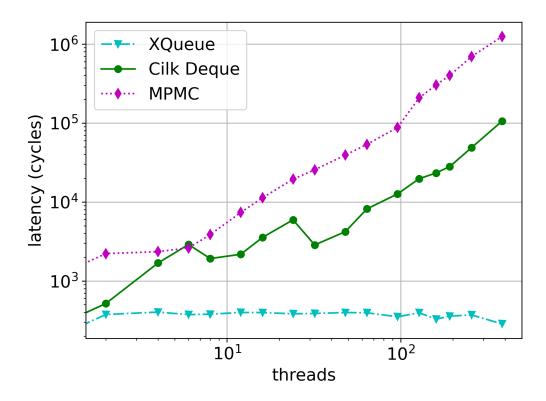

| 3.3    | Latency Comparison                                                                                                                                                                                               | 37   |

| 3.4    | Throughput Comparison                                                                                                                                                                                            | 38   |

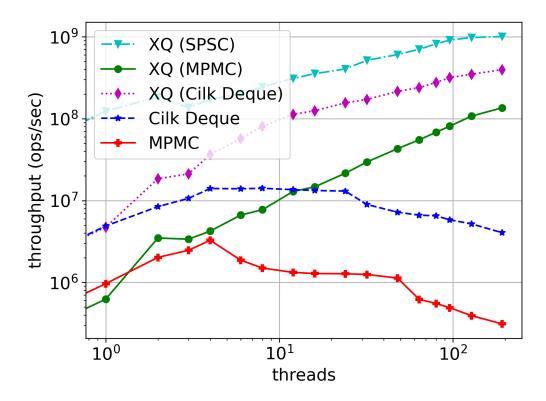

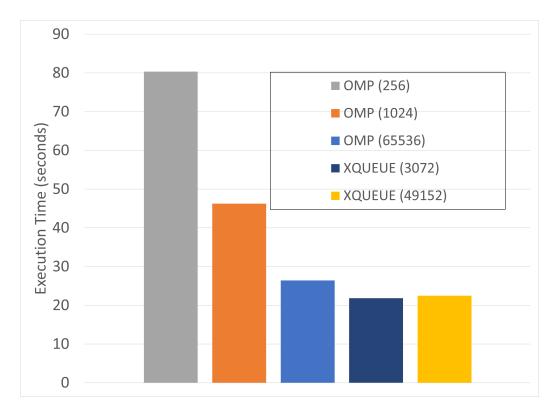

| 3.5    | Execution Time (using 192 threads) of a synthetic benchmark with a mix of fine-grained and coarse-grained tasks and varying queue sizes (legend shows queue sizes in parentheses)                                | 40   |

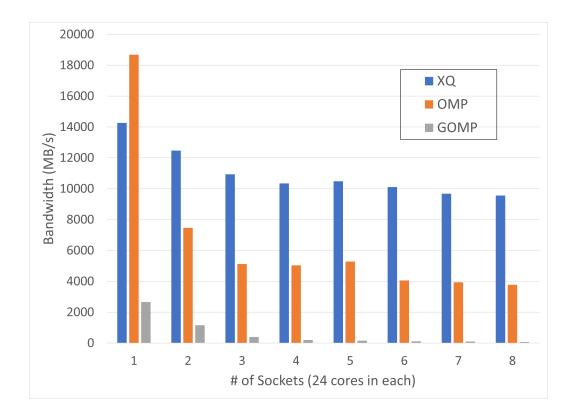

| 3.6    | Memory Bandwidth obtained using STREAM Triad benchmark                                                                                                                                                           | 41   |

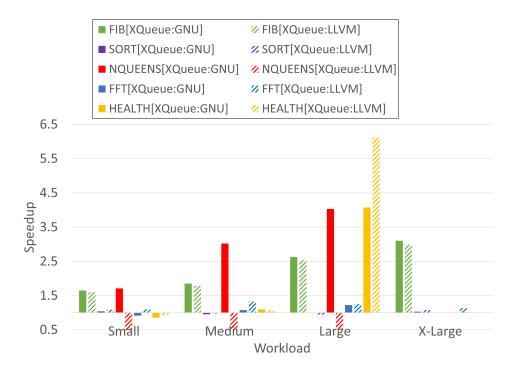

| 3.7    | Speedup of XQueue over standard GNU and LLVM OpenMP implementations on the BOTS benchmarks on skylake-192 using 192 threads.                                                                                     | 44   |

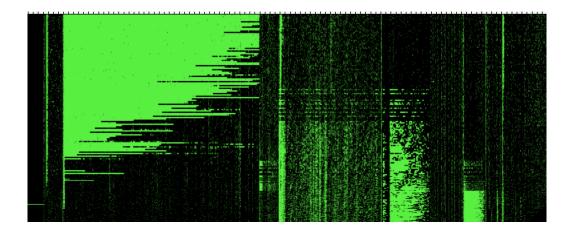

| 3.8  | Load balance of FFT on skylake-192                                                                                                                                                | 45 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.9  | Performance of Strassen's Matrix Multiplication benchmark using 8K matrices on skylake-192 using 192 threads and varying tile sizes (lower is better).                            | 46 |

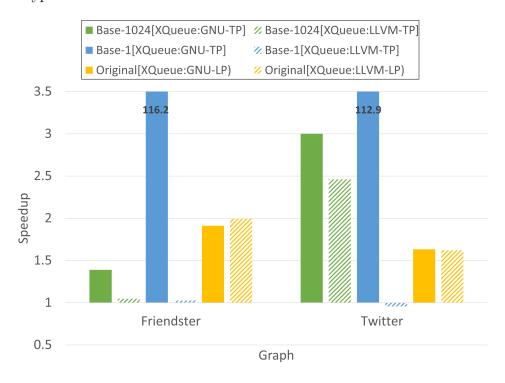

| 3.10 | Speedup of XQueue over standard GNU and LLVM OpenMP implementations when applied to Breadth First Search from GAP Benchmark Suite on skylake-192 using 192 threads                | 48 |

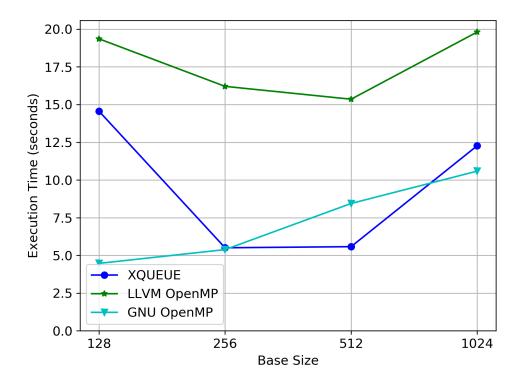

| 3.11 | Performance of Gaussian Elimination algorithm using 16K matrix on skylake-192 using 192 threads and varying base sizes (lower is better)                                          | 49 |

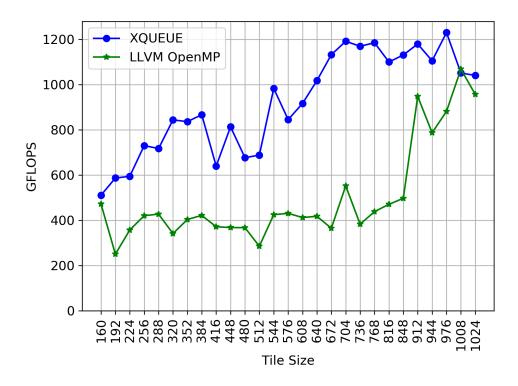

| 3.12 | Performance of Symmetric Rank Update (DSYRK) on skylake-192 using 192 threads and varying tile sizes (lower is better)                                                            | 50 |

| 4.1  | Load Imbalance in Unbalanced Tree Search using 192 threads and GNU OpenMP                                                                                                         | 54 |

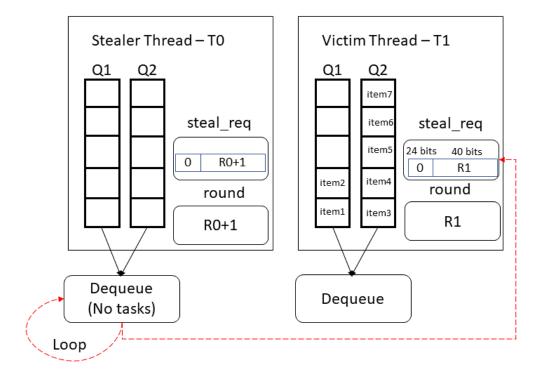

| 4.2  | Wait-free work stealing in action - [A] shows the stealer putting a steal request to the victim [B] shows the victim serving the steal request                                    | 62 |

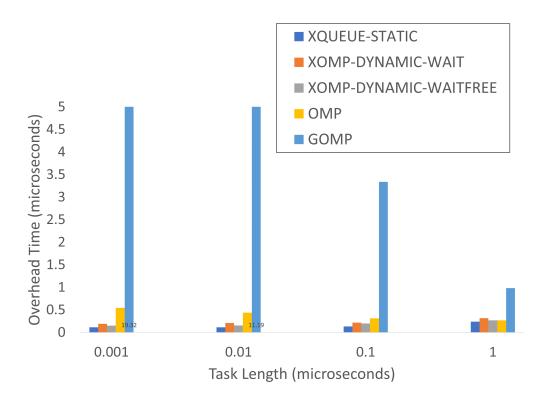

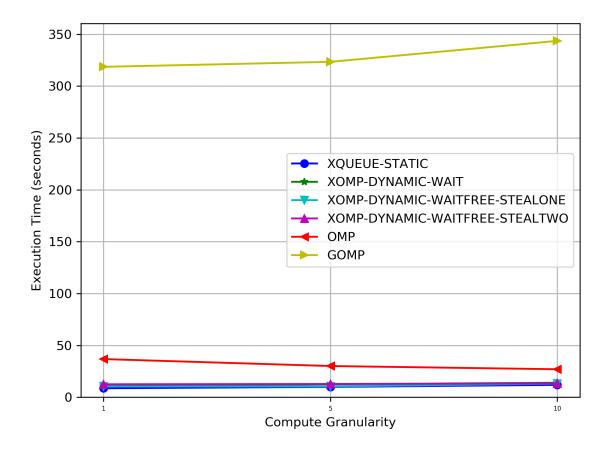

| 4.3  | Parallel Tasking Overhead on skylake-192 using 192 threads (lower is better)                                                                                                      | 66 |

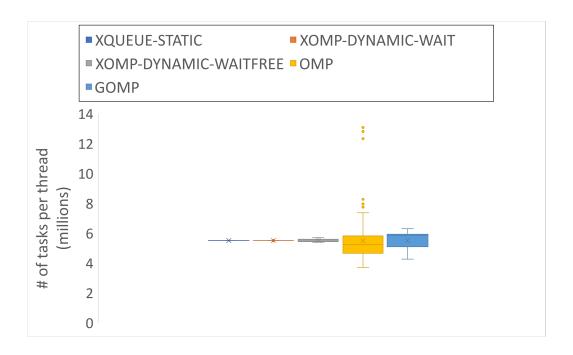

| 4.4  | Task Distribution on skylake-192 using 192 threads                                                                                                                                | 67 |

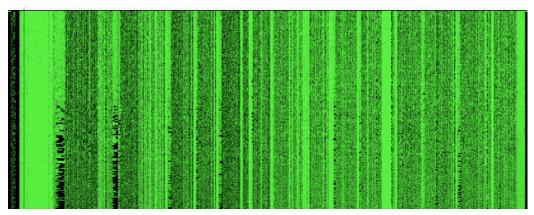

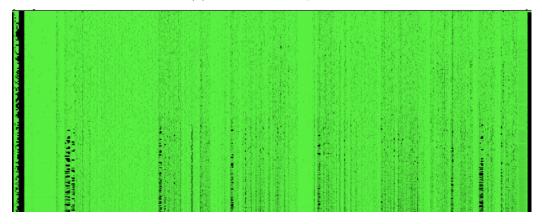

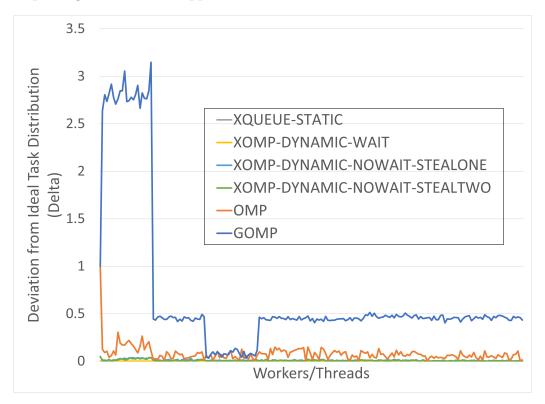

| 4.5  | Delta of Task Distribution using Work Stealing on skylake-192 using 192 threads (lower is better)                                                                                 | 68 |

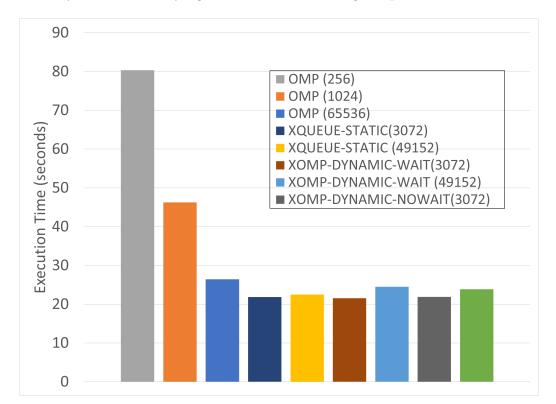

| 4.6  | Execution Time (using 192 threads) of a synthetic benchmark with a mix of fine-grained and coarse-grained tasks and varying queue sizes (legend shows queue sizes in parentheses) | 70 |

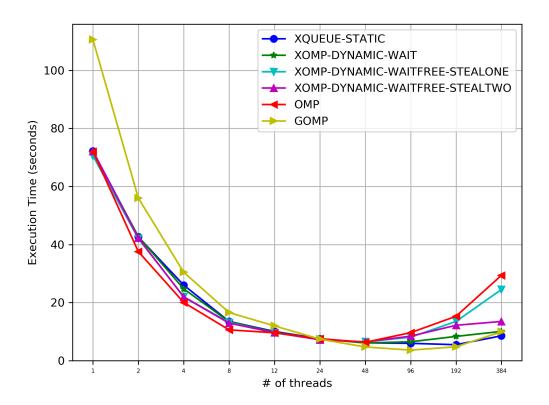

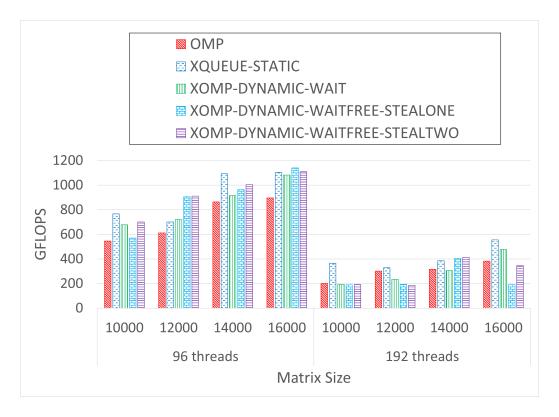

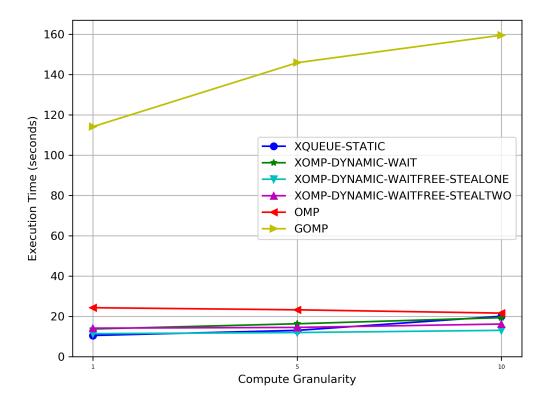

| 4.7  | Scaling of Strassen's Matrix Multiplication using 8K matrix on skylake-192 (lower is better)                                                                                      | 71 |

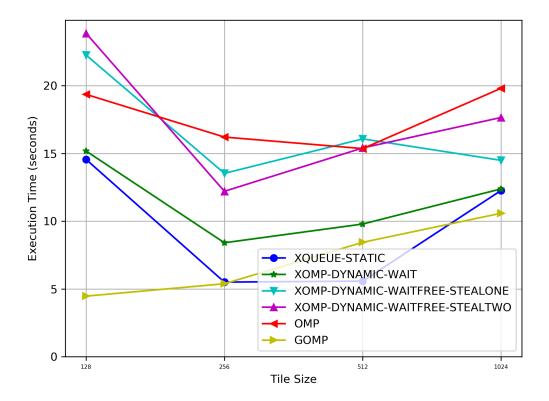

| 4.8  | Performance of Strassen's Matrix Multiplication using 8K matrix and varying base sizes on skylake-192 (lower is better)                                                           | 72 |

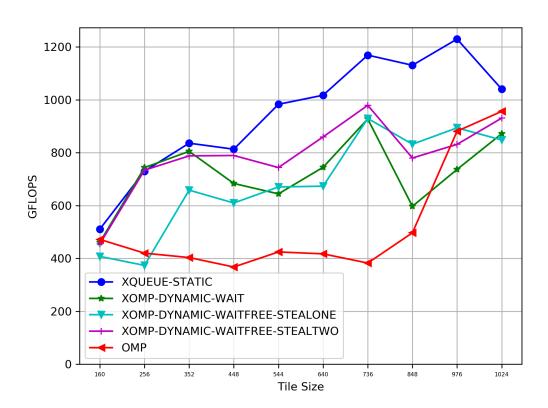

| 4.9  | Symmetric Rank Update using 12K matrix on skylake-192 using 96 threads (higher is better)                                                                                         | 73 |

| 4.10 | Cholesky Factorization on a 12K matrix on skylake-192 using 96 threads (higher is better)                                                                                         | 75 |

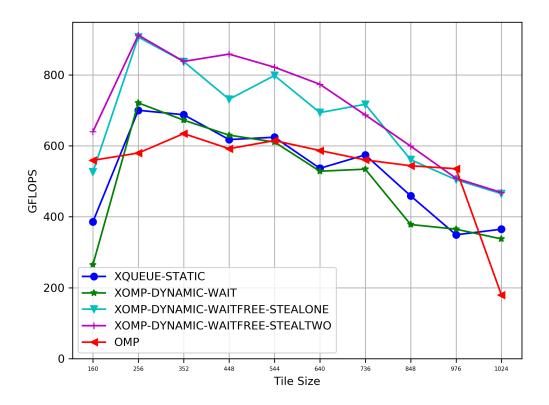

| 4.11 | Cholesky Factorization using different matrix sizes and tile size of 256 on skylake-192 run using 96 and 192 threads (higher is better) 7                                                                           |     |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| 4.12 | Unbalanced Tree Search using 96 threads on skylake-192 (lower is better)                                                                                                                                            | 77  |  |

| 4.13 | Unbalanced Tree Search using 192 threads on skylake-192 (lower is better)                                                                                                                                           | 78  |  |

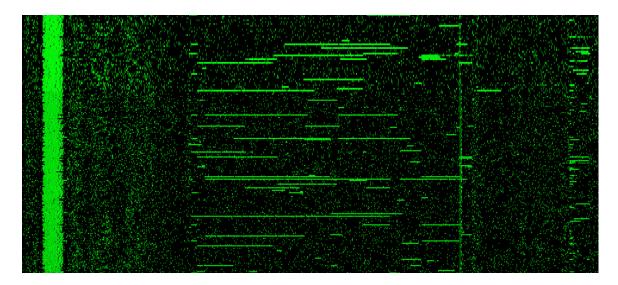

| 4.14 | Unbalanced Tree Search using X-OpenMP and 192 threads on skylake-<br>192                                                                                                                                            | 79  |  |

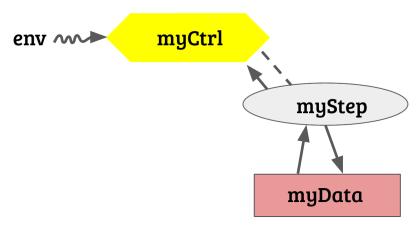

| 5.1  | Simple CnC Specification                                                                                                                                                                                            | 86  |  |

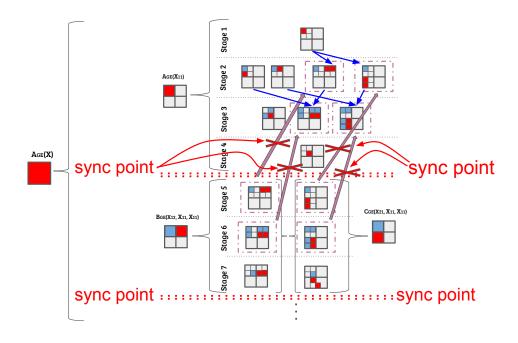

| 5.2  | A graphical representation of the CnC program                                                                                                                                                                       | 89  |  |

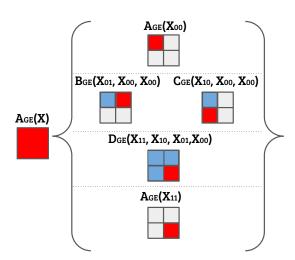

| 5.3  | Function A of 2-way $\mathcal{R}$ -DP GE algorithm                                                                                                                                                                  | 90  |  |

| 5.4  | Barriers prevent further potential parallelism                                                                                                                                                                      | 91  |  |

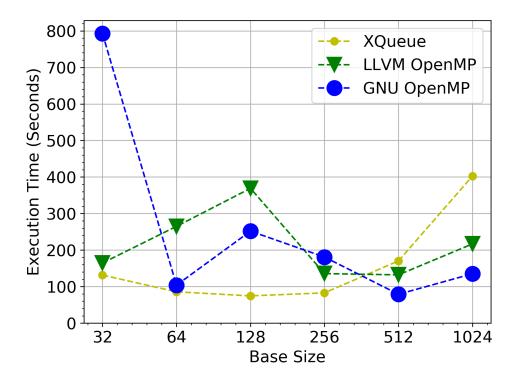

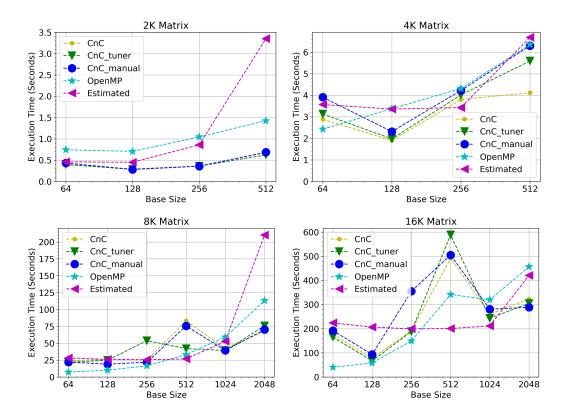

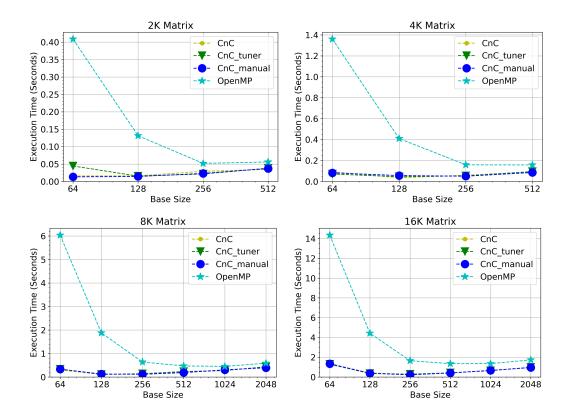

| 5.5  | Execution time of Gaussian Elimination on EPYC-64                                                                                                                                                                   | 99  |  |

| 5.6  | Execution time of Gaussian Elimination on SKYLAKE-192                                                                                                                                                               | 100 |  |

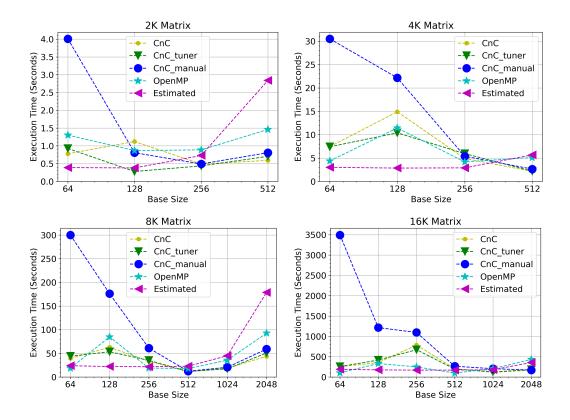

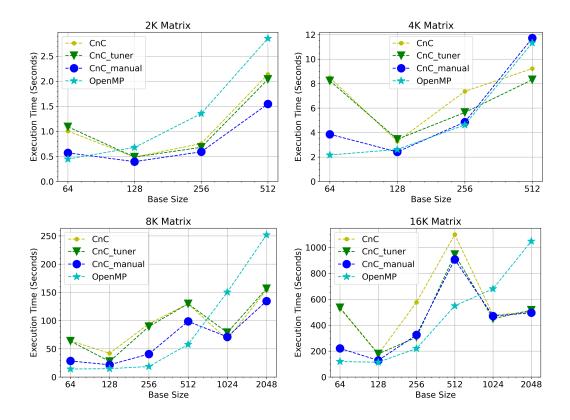

| 5.7  | Execution time of Smith-Waterman on EPYC-64                                                                                                                                                                         | 103 |  |

| 5.8  | Execution time of Smith-Waterman on SKYLAKE-192                                                                                                                                                                     | 104 |  |

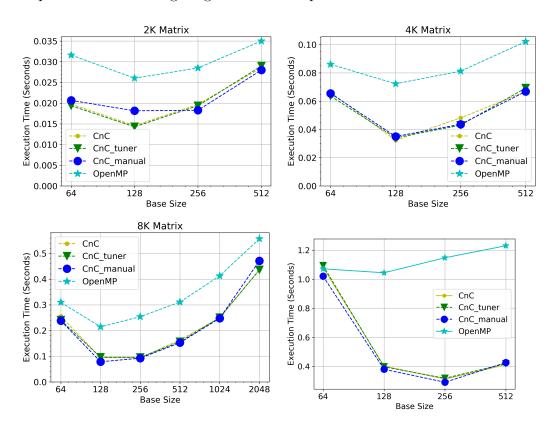

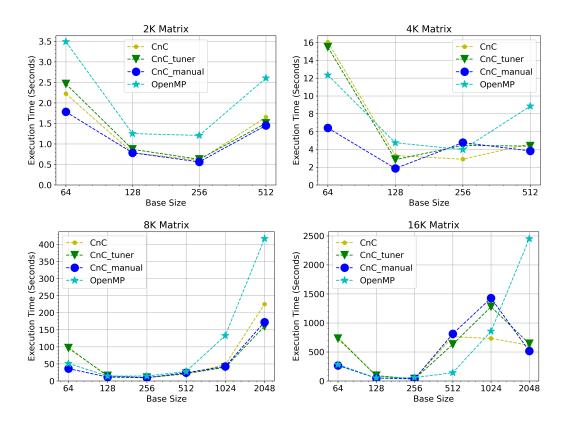

| 5.9  | Execution time of Floyd Warshall's Algorithm on EPYC-64                                                                                                                                                             | 105 |  |

| 5.10 | Execution time of Floyd Warshall's Algorithm on SKYLAKE-192 .                                                                                                                                                       | 106 |  |

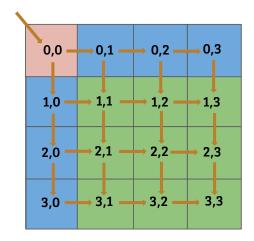

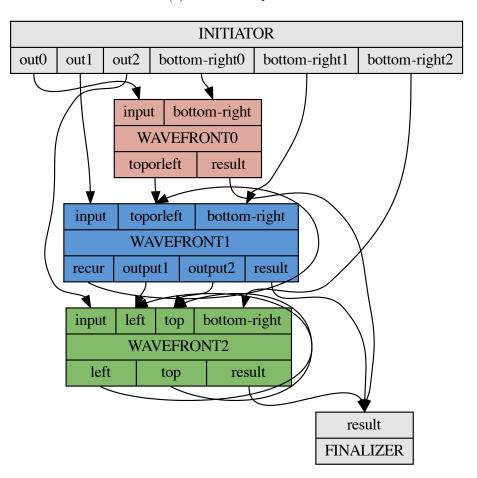

| 6.1  | 2D Wavefront Computation                                                                                                                                                                                            | 113 |  |

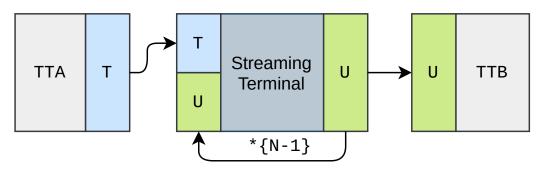

| 6.2  | TTG streaming terminal with input T, output U, and a size of N. The reduction operation of the terminal will be called $N-1$ times on input from TTA before before a task of TTB will be eligible for execution [2] | 117 |  |

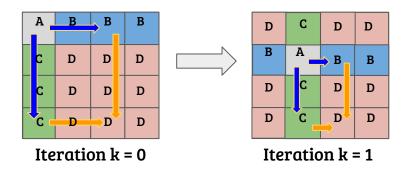

| 6.3  | Flow of data among different kernels in blocked FW-APSP algorithm.                                                                                                                                                  | 123 |  |

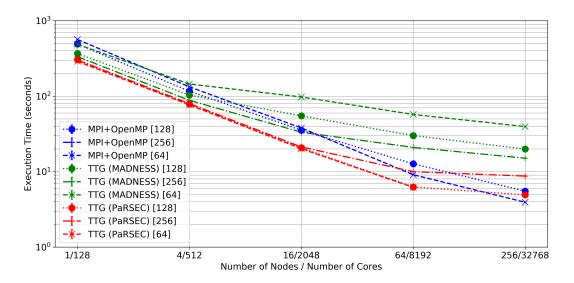

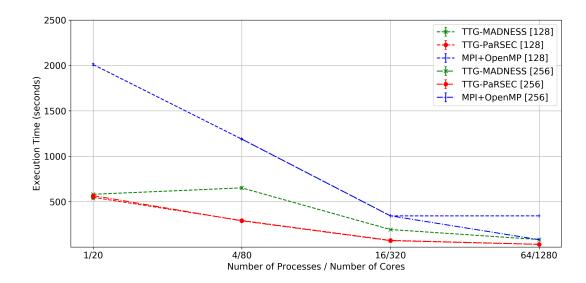

| 6.4  | Strong scaling of the Floyd-Warshall benchmark using $TTG$ and MPI+OpenMP on Hawk using 16 processes per node, 8 threads each (block sizes in square brackets)                                                      | 124 |  |

| 6.5  | Strong scaling of the Floyd-Warshall benchmark using $TTG$ and MPI+OpenMP on SeaWulf using 2 processes per node, 20 threads each (block sizes in square brackets)                                                   | 125 |  |

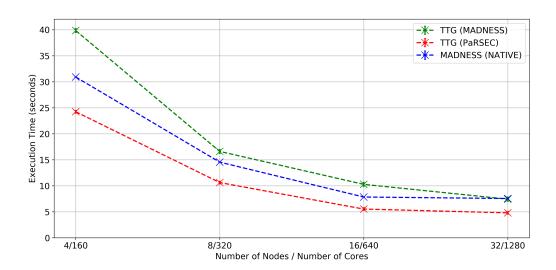

| 6.6 | Strong scaling MRA: 4 to 32 nodes with 120 functions on Seawulf, |     |

|-----|------------------------------------------------------------------|-----|

|     | using 2 processes per node with 20 threads each                  | 127 |

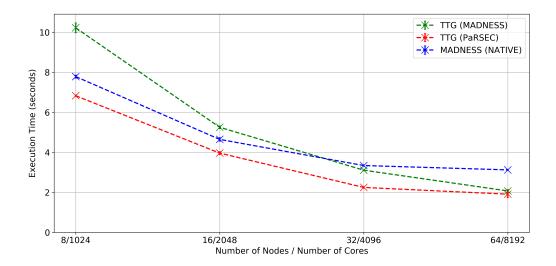

| 6.7 | Strong scaling MRA: 8 to 64 nodes with 400 functions on Hawk,    |     |

|     | using 8 processes per node with 16 threads each                  | 128 |

#### ABSTRACT

Processors with 100s of threads of execution and GPUs with 100s of cores are among the state-of-the-art in high-end computing systems. This transition to manycore computing has required the community to develop new algorithms to overcome significant latency bottlenecks through massive concurrency. Implementing efficient parallel runtimes that can scale up to hundreds of threads with extremely fine-grained tasks (less than  $\sim 100 \ \mu s$ ) remains a challenge. We propose XQueue, a novel lockless concurrent queueing system that can scale up to hundreds of threads. We integrate XQueue into LLVM OpenMP and implement X-OpenMP, a library for lightweight tasking on modern many-core systems with hundreds of cores. We show that it is possible to implement a parallel execution model using lock-less techniques for enabling applications to strongly scale on many-core architectures. While the fork-join model is suitable for on-node parallelism, the use of joins and synchronization induces artificial dependencies which can lead to under utilization of resources. Data-flow based parallelism is crucial to overcome the limitations of fork-join parallelism by specifying dependencies at a finer granularity. It is also crucial for parallel runtime systems to support heterogeneous platforms to better utilize the hardware resources that are available in modern day supercomputers. We implement Template Task Graph (TTG), a novel programming model and its C++ implementation by marrying the ideas of control and data flowgraph programming. TTG can address the issues of performance portability without sacrificing scalability or programmability by providing higher-level abstractions than conventionally provided by task-centric programming systems, but without impeding the ability of these runtimes to manage task creation and execution as well as data and resource management efficiently. TTG implementation currently supports distributed memory execution over 2 different task runtimes Parsec and Madness.

#### CHAPTER 1

#### INTRODUCTION

The Department of Energy (DOE) has reported that "Scientific productivity is one of the top ten exascale research challenges" [3]. The scientific computing community is facing unprecedented changes in computer architectures that has fueled the emergence of the many-core computing architecture. Today's high-end computing systems have 100s of processors and GPUs have 1000s of threads of execution. In a recent report [4], the DOE stated that "the transition of applications to exploit massive on-node concurrency... create the most challenging environment for developing applications in at least two decades." Extreme on-node concurrency levels of order 10<sup>4</sup> is required in order to achieve exascale performance levels according to this report. They continued by saying "much of the performance improvement must come from vectorization and lightweight tasking." These heterogeneous systems provisioned with many-core accelerators fundamentally make programmability harder as we shift from MIMD (multiple instruction, multiple data) programming to a mixture of MIMD and SIMD (single instruction, multiple data) programming. The era of many-core and exascale computing will bring new fundamental challenges in how we build large-scale systems, how we manage them, and how we program them. The techniques that have been designed decades ago will have to be dramatically changed to support the coming wave of extreme-scale general purpose parallel computing.

Today, the increase in performance of a single-threaded processor has come to an end due to the limitation of the current Very Large Scale Integration (VLSI) technology. In response, most hardware companies are designing and developing new parallel architectures [5]. To achieve higher performance, applications need to leverage the parallelism on modern architectures. On the other hand, multicore designs are also encountering scaling problems, notably the "Dark Silicon" phenomenon [6].

Power and cooling concerns suggest the number of dynamically active transistors on a single die may be greatly constrained in the near future. In other words, even if the number of transistors per chip continues to follow Moore's law, we will not be able to use all of them simultaneously. This problem may lead to scenarios in which only a small percentage of the chip's transistors can be "on" at a time [7]. The limitations of current CMOS technology has fueled the emergernce of many-core architectures and many of these massively parallel platforms offer a high ratio of performance/cost and an efficient power consumption design [8, 9, 10]. They are also widely used in high performance computing, including systems ranging from a cluster of personal computers, to large scale supercomputers. As per the Top 500 list [11], many of the most powerful supercomputers today are based on platforms that combine multi-core and many-core processors with data parallel accelerators. These many-core architectures have the potential to address the needs of computation-hungry scientific applications at the node level, but they are difficult to program due to an increasing level of parallelism that requires programmers to have a deep understanding of hardware, parallel constructs, and associated synchronization mechanisms.

Shared memory parallelism can be expressed in various forms mainly loop-based parallelism and task-based parallelism. Typically, in loop-based parallelism, loops are divided into chunks of equal size and executed concurrently by different threads managed by a parallel runtime system. Task-based parallelism evolved in parallel runtime systems to support irregular parallelism in applications where the parallelism cannot be expressed by loops. In task-based parallelism, an application is decomposed into dependent or independent tasks to form a task graph which can be executed by different threads in the system. Furthermore, task-based parallelism can be categorized based on the way task graphs are expressed: control-flow and data-flow. In control-flow, the dependent tasks can only be triggered after completion of the parent task, whereas in data-flow, the tasks are ready to run when input data

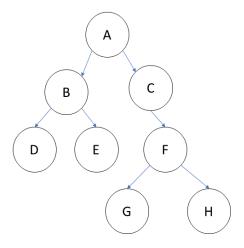

Figure 1.1. Directed Acyclic Graph (DAG)

for a task becomes available. We explore both control-flow and data-flow based task parallelism in this work.

#### 1.1 Task-Based Parallelism

Task-based parallelism is a simple paradigm for shared memory parallelism in which a computation is broken-down into a set of inter-dependent tasks which can then be executed concurrently on various cores. When a task is created by some processor or thread, it is conceptually queued for execution by a future available thread. Task dependencies and/or data dependencies are used to control the flow of tasks through the runtime system. Tasks can be modeled as Directed Acyclic Graphs (DAGs) which can dynamically unfold during the execution of the application. Given the DAG, tasks can be executed using a set of processors/threads where each thread dequeues a task from a queue and executes it. If the queue is empty, thread waits for a task to come in to the queue until the whole DAG is processed.

Figure 1.1 shows a DAG with a set of tasks with arrows showing the dependencies. Nodes at one level can ideally be executed in parallel. Here tasks D,E, G and H can be executed in parallel and they do no have dependencies since they are the

leaf tasks. Once the dependencies for F have been resolved, task F can execute. The execution models of many parallel languages and libraries [12, 13, 14, 15, 16, 17] rely on such task parallelism. Most parallel runtime systems today support execution of coarse-grained tasks with very high efficiency, however when it comes to fine-grained tasks, the efficiency decreases due to the overhead of scheduling and managing the tasks. Hence, the need for low overhead tasking becomes significant in order to explore extreme parallelism from applications.

#### 1.2 Many-Task Computing

Many-Task Computing (MTC) [18] has been an emerging paradigm and area of research for some years now. An MTC workload consists of tasks that run uninterrupted from start to completion. The task duration may be highly variable, ranging from tens of cycles to hundreds and thousands of cycles. Their dependency and data-passing characteristics may range from many similar tasks to complex, and possibly dynamically determined, dependency patterns. Many-task computing differs from high throughput computing (HTC) in the context of using large number of computing resources over short periods of time to accomplish many computational tasks. To efficiently handle MTC workloads, the system needs to exploit parallelism as much as possible. As more and more cores are being added to increase the processing speed, the need for parallel execution models that can leverage full capabilities of the processors by over-decomposition of tasks into fine-grained tasks is increasing.

#### 1.3 Early Work in Many Task Computing

GPUs have a very restrictive programming model, but provide at least an order of magnitude better throughput for applications painstakingly coded to that model. To program GPUs, typically there is a need to learn another programming language such as CUDA (NVIDIA) or OpenCL (AMD). As a result, existing vendors

must spend extra time and effort to modify or rewrite parts of their codebase to take advantage of the new capabilities provided by General Purpose GPUs (GPGPUs). Besides that, barely rewriting an application just to offload computations to a GPU rarely works well. Because of the architecture of most GPUs out there, applications must be tailored from the ground up to follow the rules of the restrictive programming model of GPUs, otherwise they may suffer from severe performance penalties. Because of that, interested vendors cannot afford to go through the effort involved. Finally, while GPUs are great for massively parallel applications with thread-switching that comes almost at no cost, their performance can take a large hit when executing programs with complex logic (like complicated branching and looping for example). Therefore they may be unsuitable for certain applications of MTC. The Intel Xeon Phi is a family of processors based on the Intel MIC Architecture [1] that incorporates earlier work on the Larrabee architecture [19]. It follows an alternative programming model that, although may not provide the same level of parallelism, provides more flexibility and therefore can be more suitable for certain application of MTC that GPUs are not suited for. The reason is that the Xeon Phi has x86 cores that are more capable (can handle complex branching and looping) than most GPU cores. Another advantage of having x86 cores is that programming the coprocessor minimizes the amount of work that needs to be done in order to integrate a Xeon Phi to an existing system. That is because the Phi does not require being programmed in any specific framework and it can natively run applications written in C with Pthreads or OpenMP. This work [20, 21] used the 22nm Knights Corner chip, which was the first commercial product from this family. This product has been discontinued due to the problems with 10nm technology and we briefly discuss our findings from using this chip.

The Knights Corner is a PCIe vector co-processor with integrates up to 61 in-order dual issue x86 cores, which trace some history to the original Pentium core,

like the Larrabee predecessor. Among other enhancements, the Corner's cores are augmented with 64-bit support, 4 hardware threads per core (resulting in more than 200 hardware threads available on a single device) and 512-bit SIMD instructions [1]. Each core has a 512KB L2 cache locally but has also access to all other L2 caches in the system through a high-speed bidirectional ring [1]. Unlike previous GPUs, the L2 cache is kept fully coherent by a global-distributed tag directory.

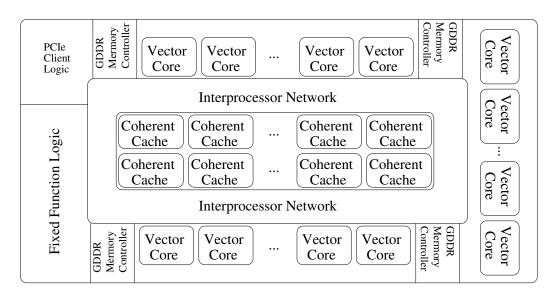

Figure 1.2. Micro-architecture of the Entire MIC coprocessor [1].

Due to the foundations of Intel architecture, the coprocessor can be programmed in several different ways. Here, we introduce two different approaches, OpenMP and SCIF (Intel's Symmetric Communications Interface). OpenMP uses offloading approach for offloading computations from the host to the accelerator. The SCIF implementation runs natively on the accelerator and accepts jobs from Clients running on the host. There are several advantages and disadvantages between the two methods. The major advantage of native execution coupled with SCIF over offloading is that the developer gets more control overall in the configuration and the architecture of their design in order to maximize performance. In addition, different MIC cards can communicate directly with each other basically making certain designs

more efficient. Frameworks that use offloading mode (*OpenMP*), do not necessarily take advantage of the DMA-features of the hardware they run on while on *SCIF* you are guaranteed that if you are using Remote Memory Access (RMA). That is not to say that *OpenMP* does not come with any advantages over *SCIF*. Quite the opposite, the advantages of offloading are pretty significant for the framework that was implemented for this project. The low-level C code needed for the *SCIF* implementation is relatively a lot more complex when compared with *pragma* directives provided by *OpenMP*. In addition, using *SCIF* implies that the framework must have at least one of its parts running natively on the Phi as the endpoint. In order to do that the developer needs to set up an application to run natively on the Phi and involves a lot of configuration. Using *OpenMP* with the offloading capabilities provided by the MIC, all this configuration is taken care of.

Figure 1.3. Micro-architecture of the Entire MIC coprocessor [1].

The OpenMP version of the framework as shown in Figure 1.3 is developed using a Producer-Consumer architecture which communicates using shared memory for IPC. The Consumer side hosts the framework which runs as multiple worker threads

which use the shared memory space as a queue structure, continuously accepting new tasks from producer. Likewise, the producer acts as a client process which submits tasks to the queue. Asynchronous offloading is used to allow the framework to be non-blocking to continue accepting tasks while other tasks are running on the Phi. This approach was chosen to provide the same feature set as GeMTC [22] while taking advantage of asynchronous offloading capabilities of OpenMP.

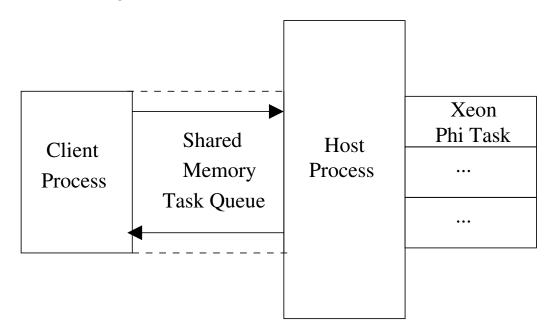

SCIF implementation employs a Client Server architecture where clients send their tasks to the Phi from the host and the server, which runs natively on the Phi, accepts the jobs. After submitting the job, the clients can request the result and the server will deliver it to them when the task has finished processing and is placed on the results queue of the framework. The whole procedure is non-blocking for the server who can handle multiple requests and submissions at the same time. That functionality is implemented with epoll() for handling connections that are later passed to threads [23] that push or dequeue tasks from the queues. The SCIF socket-like API is used for communications between the server and the clients. It comes as a shared library named \*library. This library includes all the functionality that handles incoming and outgoing queues of tasks, pushing jobs and distributing tasks to workers. It is also completely parametrizable in terms of queue sizes, worker threads, and application threads. Since the Xeon Phi does not have the hierarchical architecture of SMXs and Warps nor the concept of application kernels that you generally see in GPGPUs, everything is implemented with standard Pthreads. There is a parametrizable number of master threads that dequeues tasks from the incoming queue. If the task is a parallel application, which is the case most of the time, then the master thread will assign the task to the specified number of worker threads. Else if it is sequential only one thread will be assigned and the master thread will go back to dequeue more jobs. Each queue is implemented as a finite buffer from the Producer-Consumer model which means that it uses a single mutex and two semaphores to

Figure 1.4. Efficiency of Sleep workload using MIC by varying concurrency ensure that no deadlocks or data-races arise.

All of our experiments were run on the Midway High Performance Computing Cluster at University of Chicago. Our testing host is an Intel Sandy Bridge with 32 cores at 2.6 Ghz and 32 GB of RAM. It has 2 Xeon Phis attached to it.

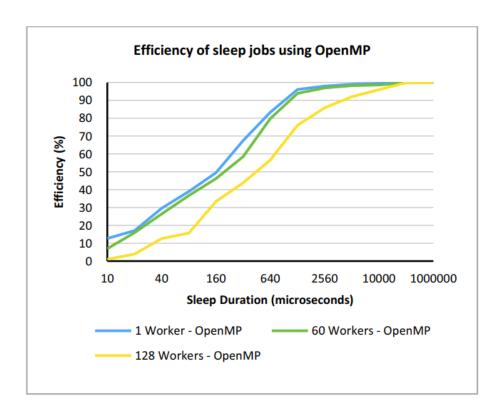

We performed experiments using a synthetic sleep workload with various sleep length tasks. As seen in figure 1.4, preliminary results show that efficiency reaches higher 90s for task lengths at 1 msec when using 1 worker on the host, 2 msec for 60 workers and 5 msec for 128 workers. This clearly shows that this framework using OpenMP performs better than GeMTC on Xeon Phi which reaches higher efficiency only at 5 ms. To reduce the overhead of multithreading, we took an approach of creating threads on the Phi before offloading tasks which reduced the overall execution time considerably. Also, figure 1.5 shows the comparison of sleep workload efficiency

Figure 1.5. Efficiency comparison of sleep workload using OpenMP and SCIF

between OpenMP and SCIF. Both implementations achieve 90% efficiency with sleep duration of 640 microseconds.

To enable running MTC workloads on Xeon Phi, we designed a framework that not only sends and executes tasks on Xeon Phi but also ensures that these tasks are isolated from each other and can run in parallel. We implemented both OpenMP as well as SCIF-based frameworks and were able to run MTC workloads on Xeon Phi.

1.4 Dissertation Overview These preliminary observations motivated us to further explore many- core architectures and fine-grained tasking with the goal to reduce the underlying overheads of the existing parallel runtime systems and to explore extreme fine-grained parallelism. Parallel execution models typically use concurrent data structures like queues to hold a bag of tasks. In Chapter 2, we shifted our focus to analyzing the performance of concurrent queues and synchronization mechanisms to understand the overheads of managing tasks in task-based runtime systems. In Chap-

ter 3, we propose a lock-less concurrent out of order queueing mechanism, XQueue, with static round-robin load balancing aimed at reducing the overheads of concurrent data structures in parallel runtime systems. We integrate the lock-less mechanism into LLVM's implementation of OpenMP to test our idea on real applications written using OpenMP. In Chapter 4, we introduce X-OpenMP which extends XQueue-enabled LLVM OpenMP and implements dynamic load balancing using lock-less work stealing. X-OpenMP library can be used to transparently accelerate applications written in OpenMP just by linking against our library. In Chapter 5, we analyze the limitations of fork-join programming model in OpenMP and compare with data-flow programming models. We show that data-flow programming models are important for expressing fine-grained parallelism in applications. In Chapter 6, we present a new data-flow based programming model TTG that aims to bridge the gap between programmer productivity and performance portability. In Chapter 7, we discuss the related work and in Chapter 8, we conclude.

#### CHAPTER 2

## HOW BAD IS CONCURRENT QUEUE PERFORMANCE ACROSS MANY THREADS?

A queue is a data structure that allows insertion of items using enqueue operation and removal of items using dequeue operation. The operations are performed in a first-in first-out (FIFO) order. A concurrent queue allows multiple producers to insert items and multiple consumers to remove items from the queue by protecting the operations using synchronization mechanisms. Concurrent queues permeate computer systems and networks. For example, Hadoop MapReduce [24] uses scheduling queues to organize applications and share resources between the running applications. Apache Spark [25] uses queues for FIFO job scheduling and can concurrently execute jobs submitted by various threads. Database Management Systems and Information Retrieval Systems often have a query execution engine that is responsible for selecting the proper selection algorithms to implement a given query plan, deciding whether intermediate results are materialized or pipelined and executing the resulting physical query plan as a parallel program. Today's TPUs [26] can be used to accelerate neural network performance; however, the input data pipeline needs to be efficient to extract data asynchronously for achieving peak performance. Multiple concurrent queues can be used for data pipelining by fetching data ahead of time thereby improving resource utilization and increasing the overall throughput.

Our focus on concurrent queues is more specifically motivated by intra-node task parallelism on modern and future parallel computers. Task parallelism is an important paradigm for shared-memory parallelism in which computation is broken down into a set of inter-dependent tasks which can then be executed concurrently on various cores. Task dependencies and data dependencies are used to control the flow of tasks through the runtime system. The execution models of many parallel languages use such task parallelism. For example, OpenMP [27] has evolved to a

task-centric model where even parallel loops are compiled to fine granularity tasks with dependencies which the run-time must dynamically schedule to the available resources. When a task is enabled by some thread, it is conceptually queued for execution by a future available thread. Software dataflow languages [14] similarly have a runtime that executes a dynamically unfolding task graph with scheduling via concurrent queues.

To achieve strong scaling and high effective levels of parallelism, today's parallel languages and execution models are also moving to finer and finer granularity tasks. One reason for this is that as core counts grow on the node, applications need to support over-decomposition (many more tasks than cores) in order to improve performance, hide latency caused by blocking on dependencies, and otherwise achieve maximum speedup [28]. This and other drivers produce the same outcome: tasks and their dependencies need to be managed at the sub-microsecond granularity. As the need for extremely low latency, high throughput concurrent queues grows, achieving them is simultaneously becoming increasingly difficult because the node itself is scaling.

Of particular interest here are single producer, single consumer (SPSC) and multiple producer, multiple consumer (MPMC) concurrent queues. The queue itself contains tasks, typically in the form of pointers (to task objects). A concurrent SPSC queue allows a single producer to enqueue while a single consumer simultaneously dequeues. An MPMC concurrent queue allows multiple simultaneous producers and consumers to queue and dequeue. While each producer and consumer is typically a software thread, the interesting case for latency and throughput is when these are mapped to non-overlapping hardware threads (logical cores) and scheduled simultaneously. We elaborate on these queues in Section 2.2, and show that simple approaches to their concurrency, while perfectly adequate at small scales, quickly fall apart as we

consider larger nodes.

Threads running concurrently in this manner can interleave instructions in many ways and a shared data structure needs to be carefully protected to avoid races. Concurrent SPSC and MPMC queues are no exception and require that their state (e.g. head and tail) be protected with a synchronization mechanism. Various synchronization mechanisms [29] exist, including mutual exclusion locks (mutexes), spinlocks, semaphores, and atomic primitives.

A second approach to concurrent queues is avoid separate synchronization by embedding race-avoidance directly into the data structure design itself. This also has the benefit of avoiding the possibility of deadlock due to misuse of synchronization primitives (e.g., lock acquisition in different orders along different codepaths). *lock-free* data structures achieve this through the use of atomic primitives, such as CAS (compare-and-swap) and Fetch-And-Add (FAA). Several libraries internally use lock-free techniques [30, 31, 32], but the literature has show that it is difficult to write lock-free code that is correct [33, 34, 35, 36]. Even more compelling are *lock-less* data structures [37], which not only avoid the use of locks, but also can avoid the need for atomic operations under certain conditions. Both lock-free and lock-less programming are challenging due instruction and memory access reordering that occurs due to the compiler and the hardware, and the need to observe the memory consistency model that is actually provided between logical cores.

How well do the basic primitives on which traditionally synchronized and lock-free/lock-less SPSC and MPMC queues build actually perform? To address this question, we evaluated the scalability of a wide range of primitives in terms of latency of throughput. A large, diverse set of hardware was used, including numerous variants of x64 from Intel and AMD, two generations of Intel Xeon Phi, ARM, and IBM Power9 (details in Table 2.1). Machines with as many as eight sockets and 384 logical cores

(hardware threads) were considered.

This work has the following contributions:

- 1. We motivate scalable SPSC and MPMC constructs from the needs of finegrained task parallelism.

- 2. We provide a detailed performance study of synchronization primitives, including mutexes, semaphores, spin locks, and atomic fetch-and-add operations, on today's largest shared-memory systems from Intel, AMD, IBM, and ARM. Systems with up to 8 sockets and 384 hardware threads are included.

#### 2.1 Baseline Queue Performance

A single producer single consumer (SPSC) array-based queue provides the lowest latency for enqueue and dequeue operations when both operations do not happen simultaneously since they do not require data synchronization, thread to thread communication and can benefit from data locality. In order to parallelize applications, concurrent queues are necessary for sharing work among various threads and a multiple producer multiple consumer (MPMC) queue is the most commonly used data structure. Thread contention, data synchronization, cache coherence and cache misses are few of the many factors that can highly impact the performance of MPMC queues limiting their scalability.

In order to show the scalability and performance of MPMC queues compared to SPSC queues, we selected five diverse systems (see Table 2.1) from the Mystic Testbed [38] that represent different architectures with large core counts. The five systems we choose to evaluate for these initial experiments are: 1) AMD Epyc, 2) ARM ThunderX, 3) IBM Power9, 4) Intel Xeon Phi, and 5) Intel Xeon Scalable Processor. More information about these systems (as well as others used in our

Table 2.1. Testbed for evaluation from the Mystic System

| Machine        | Model                   | Sockets-Cores/HT@Freq           |

|----------------|-------------------------|---------------------------------|

| skylake-192    | Intel Xeon Gold 8160    | 8-192/384@2.1GHz                |

| skylake-48     | Intel Xeon Gold 8160    | 2-48/96@2.1GHz                  |

| skylake-32     | Intel Xeon Gold 6130    | $2-32/64@2.1{ m GHz}$           |

| skylake-16     | Intel Xeon Silver 4110  | $2-16/32@2.1{\rm GHz}$          |

| phi-64         | Intel Xeon Phi 7210     | $1-64/256@1.5{ m GHz}$          |

| broadwell-16   | Intel Xeon E5-2620 v4   | $2-16/32@2.1{ m GHz}$           |

| haswell-12     | Intel Xeon E5-2620 v3   | $2-12/24@2.4{ m GHz}$           |

| epyc-64        | AMD Naples 7501         | $2-64/128@2.0{ m GHz}$          |

| theadripper-32 | AMD Threadripper 2990WX | $1-32/64@3.0{ m GHz}$           |

| ryzen-8        | AMD Ryzen 7 1700        | $1\text{-}8/16@3.0\mathrm{GHz}$ |

| opteron-48     | AMD Opteron 6168        | 4-48/48@1.9GHz                  |

| power9-40      | POWER9 EP73             | 2-40/160@3.8GHz                 |

| thunderx-96    | ThunderX 88XX ARM v8    | 2-96/96@2.0GHz                  |

work) can be found in Table 2.1.

We measured the latency and throughput of a simple SPSC array-based circular queue to identify baseline numbers for the lowest latency that can be achieved on latest many-core architectures [39]. Listing 1 shows the implementation of enqueue and dequeue operations for an SPSC queue. Experiments involve running 1 billion enqueue operations followed by a sequence of dequeues. We measured the latency of each operation and calculated the average time per enqueue/dequeue pair. Queue

Figure 2.1. Average latency of enqueue/dequeue operations on SPSC queue

size is set to the number of samples for the purposes of this evaluation. Results in Figure 2.1 show the average latency of both enqueue and dequeue operations. It can be noted that latency of any operation on queues takes 30 to 70 cycles depending on the architecture and clock frequency. This latency measurement includes a check if queue is full/empty, an increment operation on head/tail, a modulo operation on head/tail to get the position in the circular array and a copy operation to add/remove the item. Figure 2.2 represents the throughput, which is the rate at which items are being processed by the queue. For throughput experiments, we measured the total time taken for a billion enqueue/dequeue operations and calculated the throughput. Average throughput of enqueue/dequeue operations reaches 270 million operations per second on Intel Skylake 192-core machine. Although these results are significant showing excellent single threaded performance, an SPSC queue is limited because it

Figure 2.2. Average throughput of enqueue/dequeue operations in millions(M) on SPSC queue

cannot be used with more than one producer and one consumer.

Listing 2 shows the implementation of enqueue and dequeue operations for a multiple producer multiple consumer queue. The queue is implemented by using a semaphore which keeps track of free spaces in the queue and pthread\_mutex\_lock to lock the queue during enqueue and dequeue operations. This is the most common and simple way to implement a concurrent queue. We do not expect a single concurrent queue with multiple threads to scale well. This experiment aims at quantifying the poor scalability of MPMC queues using mutex locks. Each experiment enqueues and dequeues one billion items using equal numbers of producer and consumer threads. For all the experiments, a round robin pinning of threads is employed with producer and consumer thread being on the same core and different hyper threads. Binding threads to processors can result in better cache utilization, thereby reducing costly

```

void enqueue(int item, struct queue *q)

1

2

q\rightarrow tasks[(++q\rightarrow rear) \% q\rightarrow capacity] = item;

3

return;

4

5

6

int dequeue(struct queue *q)

7

9

return item;

10

11

```

Listing 1. Single Producer Single Consumer Queue Operations

```

void enqueue(int item, struct queue *q)

1

{

2

sem\_wait(\&q \!\!-\!\!> \!\!spaces\_sem\ )\,;

3

pthread_mutex_lock(&q->lock);

4

q->tasks[(++q->rear) \% q->capacity] = item;

5

pthread\_mutex\_unlock(\&q\!\!-\!\!>\!\!lock);

6

sem_post(&q->task_sem);

7

8

return;

10

11

int dequeue(struct queue *q)

12

13

int item;

14

sem_wait(\&q->task_sem);

15

pthread_mutex_lock(&q->lock);

16

item = q \rightarrow tasks[(++q \rightarrow front) \% q \rightarrow capacity];

17

pthread_mutex_unlock(&q->lock);

18

sem_post(&q->spaces_sem);

19

20

return item;

21

22

```

Listing 2. Multiple Producer Multiple Consumer Queue Operations

Figure 2.3. Average latency of enqueue/dequeue operations on a lock-based queue. This graph is shows that simple lock-based queues don't scale beyond 8 threads on any modern processors.

memory accesses. This thread placement is a result of tests performed by pinning producer to core 0 and consumer to each other core available and evaluating the performance obtained for every combination which resulted in separate hyper threads on the same CPU giving the highest performance.

Figures 2.3 and 2.4 show the latency and throughput, respectively. Our results indicate that latency can reach up to millions of cycles under high contention, and throughput can drop down to as low as 311,329 operations per second (aggregate over all threads). For the skylake-192 system, which had the best single core performance at 270 million operations/sec, the MPMC approach yielded only 810 operations per second per thread at a 384-thread scale (a 333,333× loss of performance). The fastest MPMC queue throughput at any scale reached just 5 million operations/sec. These

Figure 2.4. Average throughput of enqueue/dequeue operations on lock-based queue. This graph shows that the throughput of a simple lock-based queue plateaus beyond 8 threads on modern processors

results provide enough motivation to investigate methods to exploit full concurrency on many-core architectures while not compromising on the lowest latency that can be achieved.

#### 2.2 Analysis of Synchronization Mechanisms

This section conducts a detailed performance study [40] of synchronization mechanisms: 1) mutexes, 2) semaphores, 3) spin locks, and 4) atomic fetch-and-add operations. The evaluation is conducted on a testbed of 13 systems representing today's largest shared-memory systems from Intel, AMD, IBM, and ARM with up to 384 hardware threads.

2.2.1 Testbed, Software Stack, and Timing Mechanisms. Testbed: Table 2.1 shows details of the testbed used for experiments in this paper. The testbed covers latest many-core architectures from Intel, AMD, IBM and ARM with processors such as Haswell, Broadwell, Skylake, Phi, Opteron, Ryzen, Threadripper, Epyc, Power9, and ThunderX. The smallest system is an 8-core single socket system from AMD. The largest system is an 8-socket system with 24-core Intel CPUs, for a total of 192-cores and 384 hardware threads. The average system scale is about 50-cores and 100 hardware threads.

**Software stack:** All experiments in this paper are performed on Ubuntu 18.04 operating system and compiled using GCC version 7.3 with O2 optimization level.

Fine-grained timing: On x86 architectures, latency is measured in CPU cycles using RDTSCP instruction for start time and RDTSC + CPUID instruction for the end time. RDTSCP is a serializing instruction and it prevents instruction reordering around the call. CPUID is also a serializing call and when it follows RDTSC instruction, it prevents any future instructions to be executed before timing information is read. The combination of these two timing functions gives the most accurate results for latency. Timing on ARM and Power9 architectures is quite different from x86 architectures. ARM processor has a PMU cycle counter which is only accessible in privileged mode. The operating system sets up a virtual counter which counts at the same frequency as the physical counter and can be used for fine-grained measurements. The ARM cycle counter ticks at a lower frequency than the frequency that cores are running at and hence calibration is required to get the multiplier that needs to be applied to the cycle count to get a precise value. In Power9, time base register counts cycles at a fixed lower frequency and needs to be calibrated to convert the value to actual cycles at CPU clock frequency. Throughput in all experiments in this

paper is measured using CLOCK\_MONOTONIC for start and end times. Throughput is calculated for each thread individually and all the results are aggregated to get the final throughput value for the experiment.

2.2.2 Performance of Synchronization Mechanisms. In order to program for shared-memory systems using multithreading, threads need to be synchronized. Various thread synchronization mechanisms exist which ensure that threads do not simultaneously execute a critical section of the program. Many languages provide high level abstractions for synchronization to ease parallel programming. Common synchronization mechanisms include mutexes (mutual exclusion locks), semaphores, reader/writer locks and condition variables. Mutex is a mutual exclusion lock which ensures exclusive access to the shared resource. Spinlock is a type of lock which waits in a busy loop if lock cannot be acquired. Atomics operations are instructions supported by hardware and they lock the memory bus to access the shared resource. These operations are inherently atomic and have limited support for data types on various architectures. Semaphores is a type of mutual exclusion where a thread can wait to get access to the critical section or do a post so other threads can get access.

While it is essential to synchronize data between threads, it can easily get very expensive at higher levels of concurrency. This is due to the reason that only one thread can hold exclusive access to the critical section and all other threads are waiting to get the lock using up CPU cycles. Lock-free approaches using atomic operations are believed to be highly efficient, but are hard to implement and maintain. Lock-free algorithms can be implemented by using special hardware primitives such as CAS (compare and swap), FAA (fetch and add) and LL/SC (load-link/store conditional). Most implementations of mutexes are built on top of atomic instructions supported by hardware.

The primary focus here is to analyze the cost of low-level thread synchroniza-

```

for (int i = 0; i < NUM_SAMPLES_PER_THREAD; i++)

{

lock();

counter++;

unlock();

}</pre>

```

Listing 3. Single Producer Single Consumer Queue Operations

tion mechanisms and for this purpose, we benchmarked pthread\_mutex, sem\_wait/sem\_post, fetch—and—add and spin\_lock/spin\_unlock to measure latency. Spinlock for this benchmark is implemented using test-and-set algorithm using CAS atomic primitive. Fetch-and-add is supported by x86 architectures using 'lock xadd' instruction. The Power9 variant for FAA instruction is 'lwarx/stwcx' and ARMv8 provides 'ldxr/stxr' which are load/store exclusive instructions used for implementing atomic read, modify, write operations. These benchmarks are obtained by running a loop of 1 billion operations and collecting the aggregate of the results. As shown in Listing 3, each iteration acquires the lock, increments a shared integer and releases the lock, excluding fetch-and-add which performs an increment operation atomically.

Figure 2.5 shows that all synchronization mechanisms exhibit higher latencies due to contention at higher levels of concurrency. There are many factors that impact the cycle counts like cache coherence, communication latency between cores on same and different sockets, interrupts, cache misses, etc. Hence, it is important to run multiple iterations of these benchmarks and to compute the average number of CPU cycles to estimate the latency of these operations. Latency of a single atomic increment on a Skylake system with 192-cores and 384 hardware threads when running on all threads concurrently is 33592 cycles whereas on Intel Xeon Phi Knights Landing with 64-cores and 256 hardware threads, latency reaches 3868 cycles. Similar behavior is observed on other architectures with latencies reaching up to thousands

Figure 2.5. Average latency of incrementing an integer using different synchronization mechanisms. Same trend is observed on all architectures where latency keeps increasing as threads are scaled up except Intel Xeon Phi.

of CPU cycles solely for acquiring the lock, incrementing a variable and releasing the lock.

Although AMD, Intel, ARM and IBM have distinctly different architectures, it is interesting to note that the latency of synchronization mechanisms steadily increases on all the architectures as concurrency increases. For atomic instructions, most architectures show a slow rise in the latency up to 8 threads and latency linearly increases after 8 threads whereas for mutex, spinlock and semaphor, latency steadily goes up as concurrency level increases. Intel Broadwell, Haswell and Skylake processors exhibit similar performance curve as threads are scaled up where as AMD Ryzen, AMD Threadripper and AMD Epyc processors start with a slow increase in latency up to 8 threads for all four types of locks and then the latency rapidly grows as level as concurrency increases.

Intel Xeon Phi Knights landing with 64-cores shows interesting results. Although latency increases up to 64 threads, the latency remains constant as more threads are added. This behavior can be attributed to the round robin hyperthreading implemented in Intel Xeon Phi (which is different than all the other processor architectures evaluated in this paper). In x86 architectures, hyper-threading allows each physical processor to be perceived as two separate logical processors within the operating system by sharing the resources, which results in both hyper-threads running simultaneously increasing contention on each core. Whereas, in Intel Xeon Phi, every core alternates scheduling hardware threads at each cycle thereby not increasing contention and resulting in a better performance as threads are scaled up to more than the number of cores [41].

## 2.3 Summary

We were not surprised by these findings as it is well known that state-of-the-art

synchronization mechanisms do not scale beyond single digit concurrent threads [42]. These limitations are automatically imposed onto concurrent data structures that are implemented using such synchronization mechanisms. Furthermore, use of such concurrent data structures in modern parallel runtimes have significant overheads for managing extremely fine-grained tasks. Even though at low concurrency these mechanisms only cost hundreds of cycles, these costs quickly grew to tens of thousands and even hundreds of thousands of cycles at hundreds of threads. Our experience with the cost of synchronization mechanisms at high concurrency along with the cost of MPMC queues as a building block for parallel runtimes has motivated our investigation into methods to eliminate synchronization mechanisms in order to unleash the full performance of many-core architectures under high concurrency.

#### CHAPTER 3

# SCALABLE CONCURRENT QUEUES ON MODERN MANY-CORE ARCHITECTURES

This work is motivated in large part by the significant latency gap observed with SPSC and MPMC models. From the results presented in Section 2.2, it is clear that having a single lock across all threads is not scalable and severely limits parallelism across many threads. Using more locks is a better alternative which will result in less contention and allow for more fine-grained parallelism. However, more locks also means more CPU cache flushes to maintain cache coherency, which could adversely impact the performance of locking code. A balanced locking scheme with fewer locks (or no locks if possible) can support an ever increasing amount of parallelism in concurrent programming. The key idea behind this work originates from the significant loss in performance of MPMC queues as compared to SPSC queues as observed in Section 2.1.

A simple concurrent SPSC queue can enqueue and dequeue items in less than 100 cycles. Independent SPSC queues per core could, in theory, scale linearly with increasing core counts. Thus, we believe that an MPMC lock-less queue can be built using SPSC queues by manipulating the task or data flow carefully.

We make the following contributions in this chapter:

1. We design and implement XQueue [39], a lock-less, relaxed-order MPMC queue that uses multiple queues for improved locality without using locks or atomic operations. We demonstrate the scalability of XQueue using microbenchmarks measuring latency as low as 110 cycles and throughput as high as 1 billion ops/sec across today's largest shared-memory systems from Intel, AMD, IBM, and ARM up to 192-core scales. These numbers represent 6900X lower latencies and 3300X higher throughput compared to existing MPMC queue implementations.

2. We integrate XQueue into LLVM OpenMP and evaluate the performance improvements on 6 unmodified applications (Fib, FFT, Multisort, NQueens, Health and Strassen) from the Barcelona OpenMP Task Suite (BOTS) as well as the breadth first search (BFS) application from the GAP benchmark suite, Gaussian Elimination algorithm and Symmetric Rank Update kernel from the PLASMA numerical library [43]. We show that the combination of XQueue and LLVM OpenMP is capable of delivering better scalability for fine-grained task-parallel workloads with up to 6× speedup compared to native LLVM OpenMP and 1× to 4× speedup compared to GNU OpenMP in most cases, and up to 116× speedup in some cases.

# 3.1 XQueue: Lock-less Queueing Mechanism for Task-Parallel Runtime Systems

We introduce XQueue [39], a novel lock-less MPMC, out-of-order queuing mechanism that can scale up to hundreds of threads. XQueue uses B-queue [44] as a building block. B-queue is a concurrent SPSC lock-free queue designed for efficient core-to-core communication. It is implemented without using any locks, atomic operations, or barriers. The latency of queue operations in B-queue is as low as 20 cycles. B-queue uses batching where both producer and consumer detect a batch of available slots that are safe to use. Batching avoids shared memory access and therefore improves performance. Several fast SPSC queues have been proposed in recent years [45, 46, 47] and we aim to demonstrate that XQueue can be built with any fast and scalable SPSC queue.

Figure 3.1 shows the architectural of XQueue on a 4-core system. The key idea here is to have N SPSC concurrent queues per worker if there are N workers. There is one master queue and N-1 auxiliary queues per worker, with N (equal to number of workers) producers adding items into master queues. Every item is a void pointer

Figure 3.1. Architecture of XQueue on a 4-core machine with 4 queues per consumer.

that represents a task where a task could be a function pointer or data pointer. One worker exists for dequeueing tasks from the master queue as well as the auxiliary queues. A worker first tries to dequeue a task from the master queue. If a task is dequeued successfully, it is processed immediately. The item when processed can generate one or more items to be enqueued into the auxiliary queues of the other CPU cores. Every worker distributes work to auxiliary queues in a round-robin fashion as shown in Figure 3.1. A worker then tries to dequeue an item from its auxiliary queues and dequeued items are processed immediately.

A simplified version of pseudocode for worker logic is outlined in Listing ??. Since all queues in XQueue are concurrent SPSC queues, producer and consumer threads can act concurrently processing items in the queues. The strategy of distributing work across queues (as shown in Figure 3.1) ensures that there is a only a single producer and single consumer for every queue at any point in time. Due to this design, locks can be completely avoided thereby reducing the latencies of queue operations and improving overall performance.

#### Algorithm 1: Worker logic

```

Input: id \leftarrow coreId;

Input: next \leftarrow nextCoreId;

1 while 1 do

ret \leftarrow dequeueFromMaster(id, item);

2

if ret = SUCCESS then

3

retItem \leftarrow processItem(item);

4

if retItem \neq NULL then

5

enqueueToAuxiliary(next, retItem);

ret \leftarrow dequeueFromAuxiliary(id, item);

7

if ret = SUCCESS then

8

retItem \leftarrow processItem(item);

if retItem \neq NULL then

10

enqueueToAuxiliary(next, retItem);

11

next \leftarrow (next + 1)\%numCores;

12

if next == id then

13

next++;

14

```

3.1.1 Load balancing. In most parallel programming systems, it is a common scenario to use multiple queues, one per worker, with work produced and consumed locally by the workers/threads. Load balancing is commonly achieved by using techniques like work stealing [48, 49]. While XQueue also uses multiple queues, it balances load by the virtue of its design with N queues per core and consumer threads inserting items into the auxiliary queues of all the other cores. This architecture enables distribution of task graphs to multiple threads with minimal overhead due to the lock-less design as compared to the state-of-the-art work stealing techniques which primarily use locks or atomics to achieve synchronization.

In a task-parallel program, tasks can be modeled as a Directed Acyclic Graph (DAG) which can be traversed based on inter-dependencies between the tasks. Task graphs have a pool of ready tasks which can be processed by threads and subtasks can be generated. The master and auxiliary queues and the communication between them is modelled after the dynamic execution of a program where a task can generate

subtasks. In the case of XQueue with N workers and N queues per worker, as shown in Figure 3.1, we employ a ring buffer topology for communicating between queues. Essentially, the consumer thread of every set of queues acts as a producer thread of N-1 auxiliary queues of all the other threads. This pattern of task distribution ensures optimal load balancing in terms of the number of tasks processed per worker. However, this may not be the best fit for every scenario for various reasons, such as data locality, task dependencies, and per task execution time. Optimal allocation of work among various threads is known to be NP-hard, but, in the case of XQueue, depending on the nature of work, the topology of connections between queues and task distribution strategy can be changed to achieve best performance.

The load balancing mechanism in XQueue can be considered as a push-based mechanism as opposed to pull-based work stealing approach. This primary difference impacts how initially imbalanced workloads are handled. For example, consider the case of Fibonacci. Execution starts with a single task which recursively unfolds the DAG as execution progresses. In the work stealing approach, idle workers randomly try to steal tasks from other workers. This results in several failed steals and coupled with the cost of locking for every steal, incurs significant overhead. On the other hand, the push-based approach of XQueue handles this efficiently with its round-robin distribution without the use of locks, thus incurring minimal overhead. We discuss the advantages and disadvantages of this approach in Section 3.2.

On modern many-core architectures, it is common to have multiple Non-uniform memory access (NUMA) zones which impact the latency of memory operations from various cores. In XQueue, every worker allocates queues in its respective NUMA zone. This ensures that any memory reads and writes from various threads have the lowest latency possible. However, when tasks propagate through auxiliary queues in the system, the latency of memory read/write is higher across NUMA

zones. With XQueue's ring buffer design across N cores with N queues, some latency is unavoidable due to the underlying architecture.

In summary, there is a lot of flexibility for defining the topology for task distribution statically and dynamically during program execution with XQueue. If the nature of the DAG and data access patterns are known, the task distribution can be tuned to achieve best performance as compared to state-of-the-art work stealing approaches.

3.1.2 XQueue Integration with the OpenMP Runtime. In order to extend our research to real systems, we integrated XQueue into OpenMP [50] to enable execution of unmodified OpenMP programs using XQueue. OpenMP's tasking model provides a way to efficiently parallelize dynamic task graphs and recursive algorithms. Several implementations of OpenMP exist: GNU OpenMP (for GCC) [51], LLVM OpenMP [50], and Intel OpenMP. We chose to integrate XQueue into the LLVM OpenMP due to its open source code and its superior performance as compared to GNU OpenMP with fine-grained tasks [52].

Implementation: In the LLVM OpenMP tasking implementation, every thread owns a queue and the enqueue/dequeue operations are protected by locks implemented using Lamport's bakery algorithm. We replaced the task queues in OpenMP with multiple SPSC queues per worker to model XQueue. OpenMP implements a work-stealing scheduler. Every thread first checks it's own queue for tasks. If no tasks are found, a thread is randomly chosen to steal a single task. We replaced the work stealing scheduler with the scheduler for XQueue as shown in Algorithm 1. In our XQueue-enabled OpenMP implementation, every thread checks its own queue for tasks. If no tasks are found, the scheduler checks all auxiliary queues. This process of checking the master queue and auxiliary queues is repeated until a termination condition is satisfied.

Optimizations: We applied few optimizations to the XQueue system during integration with the OpenMP runtime. Since the core design of XQueue is to have multiple queues per worker, at higher thread counts (hundreds), the latency of checking all auxiliary queues can become significant and reduce the overall performance. To solve this issue, we implemented a hinting mechanism where every producer stores the ID of the last queue to which the task was pushed. This hint can possibly be over-written by multiple threads writing to various queues, however this simple mechanism reduces the latency of checking auxiliary queues many times. For the applications we evaluate, this hinting mechanism gives better performance while maintaining good load balancing. We have used physical cores available on the machine for this evaluation by setting OMP\_PLACES environment variable to 'cores' and OMP\_PROC\_BIND to 'close', since not all applications can benefit from using hardware threads.

#### 3.2 Performance Evaluation

We evaluate the performance of XQueue using synthetic and real workloads. For the purposes of evaluating XQueue independently, we developed a prototype parallel runtime system that can process a dynamic task graph with task dependencies using XQueue. We first evaluate XQueue individually using a series of microbenchmarks. We deployed XQueue on 13 systems (Table 2.1); we then picked the system with the highest number of cores, the skylake-192 with 192-cores and 8 NUMA zones to conduct deeper analysis.

- **3.2.1 Experiment Setup.** We implemented three systems for the micro-benchmark evaluation:

- 1. **XQueue** (SPSC) uses a single SPSC queue per worker.

- 2. **XQueue** (MPMC) uses an MPMC queue with a master queue per worker.

3. **XQueue** (Cilk Deque) uses a Cilk deque [16] with a separate queue per worker.

Cilk deque is implemented as part of Cilk 5 multi-threaded language [16] and uses a shared-memory, mutual-exclusion protocol called the THE protocol[53] for implementing locks. This mechanism of locking is about 25% faster than hardware locking primitives.

For the macro-benchmarks, we use the XQueue-enabled LLVM OpenMP implementation with N queues per worker and N workers. We compare it with the native LLVM OpenMP and GNU OpenMP libraries.

3.2.2 Micro-benchmark Performance Results. In each experiment we perform 1 billion enqueues/dequeues concurrently by varying the number of threads. We consider a single operation to be the act of dequeing an item from the master queue and executing the function to which that item points to. The function performs a single NOP operation. The X-axis on all the figures represents the number of producers/consumers.